- Předurčení a konstrukce multiplexerů a demultiplexerů

- Realizace multiplexerů a demultiplexerů logickými obvody

Předurčení a konstrukce multiplexerů a demultiplexerů

Multiplexery (MUX)

Definice:

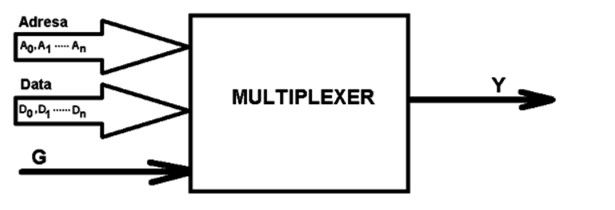

Multiplexer (MUX) je kombinační logický obvod, který umožňuje vybrat jeden z několika vstupních signálů a přenést jej na jediný výstup. Je označován také jako „datový selektor“ nebo „many-to-one“ přepínač.

Konstrukce:

- Datové vstupy: Obvykle v počtu 2n, kde nn je počet adresových (výběrových) vstupů.

- Adresové vstupy: Určují, který datový vstup bude přenesen na výstup.

- Výstup: Jeden výstupní signál.

- Blokovací (enable) vstup: Umožňuje povolit nebo zakázat činnost multiplexeru (volitelné).

Princip činnosti:

- Kombinace adresových vstupů určuje, který datový vstup je připojen na výstup.

- Multiplexery umožňují sdílení jednoho zařízení (např. A/D převodníku) více vstupy.

Použití:

- Přepínání informací mezi více zdroji a jedním výstupem.

- Převod paralelních dat na sériová (například v komunikaci po jednom vodiči)

- Realizace libovolných logických funkcí více proměnných (univerzální logický obvod).

- Optimalizace přenosových cest, snížení počtu vodičů a zvýšení efektivity systému.

Demultiplexery (DEMUX)

Definice:

Demultiplexer (DEMUX) je kombinační logický obvod, který umožňuje přivést jeden vstupní signál na jeden z několika výstupů podle adresových vstupů. Označuje se jako „data distributor“ nebo „one-to-many“ přepínač.

Konstrukce:

- Informační vstup: Jeden vstupní signál.

- Adresové vstupy: Určují, na který výstup bude signál přiveden.

- Výstupy: Obvykle , kde je počet adresových vstupů.

- Blokovací vstup: (Enable) pro povolení činnosti (volitelné).

Princip činnosti:

- Podle kombinace adresových vstupů je vstupní signál přiveden na konkrétní výstup, ostatní výstupy jsou neaktivní.

- DEMUX je často využíván jako dekodér adres nebo pro rozdělení sériového signálu na více paralelních výstupů.

Použití:

- Převod sériového signálu na paralelní.

- Ovládání více zařízení jedním signálem (adresování).

- Paměťové adresování, směrování dat v číslicových systémech.

Realizace multiplexerů a demultiplexerů logickými obvody

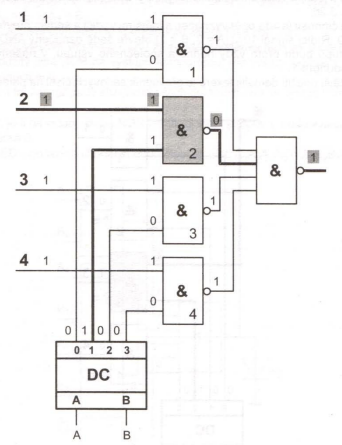

Realizace multiplexeru logickými obvody

- Základní princip: - Multiplexer lze realizovat pomocí základních logických členů (AND, OR, NOT). - Každý datový vstup je připojen na AND člen spolu s příslušnou kombinací adresových vstupů a jejich negací. - Výstupy AND členů jsou spojeny do jednoho OR členu, který tvoří výstup multiplexeru.

Příklad – 2:1 Multiplexer:

- Vstupy: D0, D1

- Adresový vstup: S

- Výstup: Y

| S | Y |

|---|---|

| 0 | D0 |

| 1 | D1 |

| Logická funkce: |

- Realizace: 2 AND členy, 1 NOT člen, 1 OR člen.

Příklad – 4:1 Multiplexer:

- Vstupy: I0, I1, I2, I3

- Adresové vstupy: S1, S0

- Výstup: Y

| S1 | S0 | Y |

|---|---|---|

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

| Logická funkce: |

-

Realizace: 4 AND členy, 2 NOT členy, 1 OR člen.

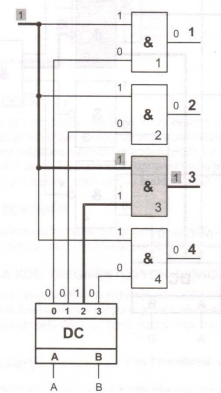

Realizace demultiplexeru logickými obvody

- Základní princip: - Demultiplexer je tvořen AND členy, každý výstup je aktivní pouze při určité kombinaci adresových vstupů. - Vstupní signál je přiveden na všechny AND členy, ale na výstup se dostane jen tam, kde jsou adresové vstupy ve správné kombinaci.

Příklad – 1:2 Demultiplexer:

- Vstup: D

- Adresový vstup: A

- Výstupy: Y0, Y1

| A | Y0 | Y1 |

|---|---|---|

| 0 | D | 0 |

| 1 | 0 | D |

Logické funkce:

- Realizace: 2 AND členy, 1 NOT člen.

Příklad – 1:4 Demultiplexer:

- Vstup: D

- Adresové vstupy: S1, S0

- Výstupy: Y0, Y1, Y2, Y3

| S1 | S0 | Y0 | Y1 | Y2 | Y3 |

|---|---|---|---|---|---|

| 0 | 0 | D | 0 | 0 | 0 |

| 0 | 1 | 0 | D | 0 | 0 |

| 1 | 0 | 0 | 0 | D | 0 |

| 1 | 1 | 0 | 0 | 0 | D |

Logické funkce:

-

Realizace: 4 AND členy, 2 NOT členy.

Rozdíly

| Vlastnost | Multiplexer (MUX) | Demultiplexer (DEMUX) |

|---|---|---|

| Funkce | Výběr jednoho vstupu na výstup | Přepnutí vstupu na jeden z výstupů |

| Vstupy | datových, adresových | 1 datový, adresových |

| Výstupy | 1 | |

| Princip | Many-to-one | One-to-many |

| Použití | Přepínání, generování funkcí, TDM | Rozdělení signálu, adresování |

| Realizace | AND, OR, NOT členy | AND, NOT členy |